# ANALYSIS OF LIMIT CYCLES IN THE DIRECT FORM DELTA OPERATOR STRUCTURE BY COMPUTER-AIDED TEST

Juha Kauraniemi

Helsinki University of Technology, Institute of Radio Communications Laboratory of Signal Processing and Computer Technology Otakaari 5 A, FIN-02150 Espoo, Finland Juha.Kauraniemi@hut.fi

### ABSTRACT

Delta operator filter structures have received interest due to good roundoff noise and coefficient sensitivity properties. However, it has been reported that delta realizations may produce limit cycles. In this paper, limit cycle problem in the direct form delta operator structure is studied by using a computer-aided test. The test determines exact amplitude and period of the maximum amplitude limit cycle, including the case where the limit cycles are absent. Using this knowledge the required wordlength to satisfy limit cycle performance specifications can be accurately determined. It is shown that with narrowband lowpass filters limit cycles, if they exist, are of much smaller amplitude than those of the traditional delay realized direct form structure.

### **1. INTRODUCTION**

When the sampling rate is high compared to the signal bandwidth the delta operator realized recursive digital filters have been found to have superior roundoff noise and coefficient sensitivity properties over the delay realizations [1-3]. However, it has been noted that when fixed point arithmetic is used, delta operator structures may exhibit limit cycles [4]. In our recent work, we studied zero input limit cycles in the transposed direct form II delta operator structure (DFIIt) [5]. It was found out that the delta structure cannot be guaranteed to be free of limit cycles by using a frequency domain criterion.

Frequency domain criteria are typically sufficient criteria, i.e., if they fail the presence of the limit cycles is not guaranteed. In addition, they don't give information about the amplitudes of the limit cycles and being based on a sector condition they are not applicable when two's complement truncation is used [5]. Many more or less simple upper bounds for limit cycles have been proposed, e.g., one in [7]. However, these bounds are typically too pessimistic and do not predict the absence of limit cycles.

In this paper, the zero-input limit cycles in the secondorder delta operator DFIIt structure are studied by using exhaustive search method [6]. This type of test can be used with any type and number of quantizations. Differing from the one presented in [6], algorithm described here determines in addition the maximum amplitude initial state and the period of the maximum amplitude limit cycle. A major drawback of the exhaustive search is that, depending on the filter, running time can be large. We propose a simple search algorithm which reduces the number of computations significantly, making the use of the exhaustive search feasible.

It is shown that limit cycles may exist in the delta direct form structure, but for a narrowband lowpass filter they are very small in amplitude. Moreover, when compared to the traditional delay realized direct form structure the limit cycle performance of the delta direct form structure is much better. In order to have low roundoff noise, it is customary to implement inverse delta operators with higher precision than input and output signals [2,3]. This increases the implementation complexity and the number of additional bits should be small. In [3] it was shown that good roundoff noise performance can be obtained by using only few bits longer precision for the inverse delta operators. Here it is shown that this type of implementation can have good limit cycle performance.

### 2. LIMIT CYCLE BOUNDS

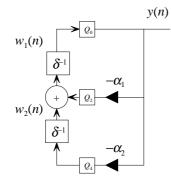

A recursive part of the second-order delta DFIIt is shown in Fig. 1, where  $\delta^{-1} = \Delta z^{-1}/(1-z^{-1})$  is the causal inverse of the delta operator and  $\Delta$  is a free parameter that can be chosen, e. g., to minimize the output roundoff noise [3]. The coefficients are related to the z-domain denominator coefficients as given in Table 1. It has been found that essential for good roundoff noise performance is that inverse delta operations are performed with higher precision than output wordlength (single precision = (B + 1) bits) [2,3]. Here inverse delta operations are performed in enhanced precision,  $(B + B_d + 1)$  bits, where  $B_d \leq B_c$  and  $B_c$  is the number of fractional bits in the filter coefficients. If  $B_d = B_c$  we call this double precision. The system under zero input is described by the difference equations:

Figure 1: Recursive part of the second-order delta DFIIt structure. Quantizations  $Q_1$  and  $Q_3$  exist in the operators if  $\Delta < 1$ .

$$y(n) = Q_0 \Big[ w_1(n) \Big]$$

$$w_1(n+1) = w_1(n) + Q_1 \Big[ \Delta \Big( w_2(n) + Q_2 \Big[ -\alpha_1 y(n) \Big] \Big) \Big], (1)$$

$$w_2(n+1) = w_2(n) + Q_3 \Big[ \Delta Q_4 \Big[ -\alpha_2 y(n) \Big] \Big]$$

where quantizer  $Q_0$  is to single precision and other quantizers are to enhanced precision. If  $\Delta = 1$  quantizations  $Q_1$ and  $Q_3$  do not exist and if double precision is used  $Q_2$  and  $Q_4$  do not exist.

When the system exhibits a limit cycle, the state variables are absolutely upper bounded by

$$M_{i} = \sum_{k=0}^{4} e_{k} \sum_{n=0}^{\infty} \left| g_{i,k}(n) \right|, \quad i = 1, 2, \qquad (2)$$

where  $g_{i,k}(n)$  is the inverse *z*-transform of the transfer function from the *k*th quantization error source to the *i*th state variable  $w_i$ ,  $e_k$  is the maximum absolute value of the error of the *k*th quantization and  $e_k = 0$  if *k*th quantization does not exist. The types of the quantizers are not limited, but in this text we concentrate on the rounding. Thus, when single precision is normalized to integers  $e_0 = 2^{-1}$  and  $e_k = 2^{-(1 + B_d)}$  for k = 1, ..., 4 if corresponding quantization exists. The error transfer functions can be solved from (1). All the error transfer functions  $G_{i,k}(z) = N_{i,k}(z)/D_{i,k}(z)$  have a common denominator  $D_{i,k}(z) = 1 + a_1 z^{-1} + a_2 z^{-2}$  for all *i*,*k* and only the numerators are given.

$$N_{1,0}(z) = -(2+a_1)z^{-1} + (1-a_2)z^{-2}, \qquad (3)$$

$$N_{2,0}(z) = -(1+a_1+a_2)/\Delta \cdot z^{-1}(1-z^{-1}), \qquad (4)$$

$$N_{1,1}(z) = z^{-1}(1 - z^{-1}), \qquad (5)$$

$$N_{2,1}(z) = -(1+a_1+a_2)/\Delta \cdot z^{-2}, \qquad (6)$$

$$N_{i,2}(z) = \Delta N_{i,1}(z), \qquad i = 1, 2, \qquad (7)$$

Table 1

Relations between the denominator coefficients of the second order delta- and z-polynomials

| $\alpha_1$ | $(2+a_1)/\Delta$ | $\alpha_2$ | $\left(1+a_1+a_2\right) \big/ \Delta^2$ |

|------------|------------------|------------|-----------------------------------------|

|            |                  |            |                                         |

$$N_{1,3}(z) = \Delta z^{-2} , \qquad (8)$$

$$N_{2,3}(z) = z^{-1}(1 + (1 + a_1)z^{-1}), \qquad (9)$$

$$N_{i,4}(z) = \Delta N_{i,3}(z), \qquad i = 1,2,$$

(10)

where  $a_i$  are the denominator coefficients of the *z*-domain transfer function. Unfortunately, the summation in (2) cannot be solved in closed form and it has to be evaluated numerically as in this paper or some upper bound approximation may be used, for example [7]. A tight bound is desirable, because it determines the number of points in the search space and the maximum period of the limit cycle.

Because a digital filter under zero input is a finite state machine, (zero input) limit cycles are always periodic. The maximum period is limited by the number of states in the search space

$$T_{\max} = (2 \operatorname{int}(M_1) + 1)(2 \operatorname{int}(M_2) + 1)2^{2B_d}.$$

(11)

It is seen that the number of bits in enhanced precision affects the amount of computations.

## 3. EXHAUSTIVE SEARCH ALGORITHM

A simple approach to search the limit cycles is to start from an initial state vector  $\mathbf{w}(0)$  and compute the filter recursion until one of the four conditions is met: 1) Limit cycle is identified. Because the input to the filter is zero and filter is time invariant (also the quantization nonlinearity is independent of time) the state of the system at step *n* completely defines the state of the system at step n + 1. So, if the state vector  $\mathbf{w}(0)$  is repeated at the time step p, we know that a limit cycle of period p has occurred. 2) The state vector has grown out from the search space. 3) The state has converged to a point that produces zero output. From (1) it is seen that output is identically zero for all  $n \ge n$  $n_0$  if  $y(n_0)$  and  $w_2(n_0)$  are equal to zero. 4) The maximum number of steps (11) has expired. The same procedure is repeated until the whole search space has been evaluated or the maximum amplitude limit cycle is identified. However, this approach would lead to a high number of computations and thus, to a long run time. Here we use an alternative method, which reduces the number of computations significantly.

The search algorithm goes as follows: After computing bounds for the state variables, an array of size (11) is re-

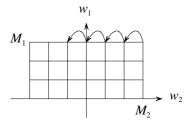

Figure 2: The search grid in the state space where  $M_1$  and  $M_2$  are bounds obtained from equation (2).

served from the memory and all its elements are initialized to zero. Before each initial state and filter recursion step it is checked if the memory location corresponding to this state is zero or not. If it is zero, a number, *trajectory number*, is written to that memory location. Different trajectory number is given for each initial state, which is not a part of some already computed trajectory. If the memory location differs from zero, the state has been already scanned and algorithm moves to the next initial state. Thread of the current initial state is as well stopped if the conditions 2) or 3) given earlier in this chapter are satisfied.

If at some time instant the trajectory number and the value in the memory are the same, a limit cycle has occurred. The period of the limit cycle is obtained by starting filter recursion from the known state of limit cycle and continuing until this state is repeated. By the same time the maximum amplitude state of the limit cycle is searched. The limit cycle is stated as a maximum amplitude limit cycle candidate, if its  $w_1$  component is larger in absolute value than that of the previous candidate (the quantized state variable  $w_1(n)$  is observed directly from the output, see equation (1)). Limit cycles are typically relatively short compared to the size of the search space. In addition, many of the initial states converge to zero or to the same limit cycle. Thus, the time penalty from recomputing the states of the limit cycle is small.

Since rounding quantization is symmetrical, i.e., Q(-x) = -Q(x) only the initial states in the upper half plane has to be searched, Fig. 2. The initial states are scanned row wise starting from  $\mathbf{w}(0) = [M_1 \times]^T$ , where  $\times$  is  $M_2$  or  $-M_2$ . When the initial state component  $w_1(0)$  is equal to the state variable  $w_1$  of the maximum amplitude limit cycle candidate, the test stops. At this point limit cycles having larger  $w_1$  component are not possible, because all those states have already been tested.

### 4. EXAMPLES

As an example sections of a narrowband fourth-order elliptic lowpass filter are studied. The *z*-domain denominator polynomials of the sections are  $D_1(z) = 1 - 1.914z^{-1} + 0.950z^{-2}$  and  $D_2(z) = 1 - 1.828z^{-1} + 0.843z^{-2}$ . Single preci-

| Table 2.           Results of the example with the delta structures |             |             |             |            |  |  |  |

|---------------------------------------------------------------------|-------------|-------------|-------------|------------|--|--|--|

| Sec                                                                 | #1          |             | #2          |            |  |  |  |

| $B_d$                                                               | 7           | 3           | 7           | 3          |  |  |  |

| $\Delta$                                                            | 1           | 0.25        | 1           | 0.25       |  |  |  |

| NG (dB)                                                             | 1.51        | 2.85        | 0.57        | 1.64       |  |  |  |

| Period                                                              | 155         | 1           | 216         | 1          |  |  |  |

| Output                                                              | $1/2^{7}$   | 0           | $1/2^{7}$   | 0          |  |  |  |

| $w_1(0)$                                                            | $66/2^{14}$ | $3/2^{10}$  | $64/2^{14}$ | $3/2^{10}$ |  |  |  |

| $w_2(0)$                                                            | $4/2^{14}$  | $-1/2^{10}$ | $1/2^{14}$  | $1/2^{10}$ |  |  |  |

| Time (s)                                                            | 0.19        | 0.06        | 0.03        | 0.03       |  |  |  |

|                                                                     |             |             |             |            |  |  |  |

| Table 3.                                            |      |        |            |            |            |  |  |  |  |

|-----------------------------------------------------|------|--------|------------|------------|------------|--|--|--|--|

| Results of the example with the delay DFI structure |      |        |            |            |            |  |  |  |  |

| Sec                                                 | NG   | Period | Output     | $w_1(0)$   | $w_2(0)$   |  |  |  |  |

| #1                                                  | 24.4 | 1      | $12/2^{7}$ | $12/2^{7}$ | $12/2^{7}$ |  |  |  |  |

| #2                                                  | 23.4 | 1      | $32/2^7$   | $32/2^7$   | $32/2^7$   |  |  |  |  |

sion wordlength is eight bits and coefficients of the delta realizations are quantized to seven fractional bits plus a sign bit. Simulation results for two different delta configurations are shown in Table 2, where also noise gain (*NG*) values for the  $L_{\infty}$  -scaled sections are included. In the fifth row is the amplitude of the limit cycle at the output and  $w_1(0)$ ,  $w_2(0)$  are the initial states of the limit cycle.

In the first delta realization double precision and in this case roundoff noise optimal  $\Delta = 1$  is used [3]. Amplitude of the limit cycle in the output of the filter is only one least significant bit (LSB) with both the sections, see Fig. 3 and 4. In the second configuration, the parameter  $\Delta$  is likewise chosen to minimize the output roundoff noise. Three additional bits are needed to keep the noise increase under 3 dB when compared to the double precision system [3]. In these cases the period one limit cycles are internal, i.e., they are not seen at the output. In a delay realization resulting limit cycle is a DC or period one limit cycle with both the example filter sections, Table 3.

The run times of the test are included in Table 2. Test was written in the C programming language and run in a PC-computer with the Intel Pentium 120 MHz processor.

### **5. CONCLUSIONS**

We studied the limit cycle problem in the direct form delta operator structure using computer-aided test. A fast exhaustive search algorithm was proposed. It was found that narrowband lowpass systems may sustain very small amplitude limit cycles and performing inverse delta operations in less than double precision does not necessarily decrease the performance. In fact, with our example filter, the enhanced precision structure with roundoff noise optimal  $\Delta$  parameter is free of zero input limit cycles. With

Figure 3: The maximum amplitude limit cycle in the section #1. a) The filter output (solid line), the state variable  $w_1$  (dashed line) and the state variable  $w_2$  (dotted line). Single precision is normalized to integers. b) The limit cycle in the state space. Double precision is normalized to integers.

narrowband lowpass filters the delta operator structure is superior to the delay structure in the limit cycle performance.

#### ACKNOWLEDGMENTS

The author wishes to thank Prof. Timo I. Laakso for helpful discussions and comments on this manuscript. This research work is funded by Technology Development Centre, Nokia Corporation, Telecom Finland and Helsinki Telephone Company. It is also supported by Foundation of Technology.

### REFERENCES

[1] G. C. Goodwin, R. H. Middleton, and H. V. Poor, "High speed digital signal processing and control," *Proc. IEEE*, Vol. 80, pp. 240-259, Feb. 1992.

Figure 4: The maximum amplitude limit cycle in the section #2.

- [2] J. Kauraniemi, T. I. Laakso, I. Hartimo, and S. J. Ovaska, "Delta operator realizations of recursive digital direct form filters," in *Proc. ECCTD* '95, Vol. 2., pp. 667-670, Istanbul, Turkey, Aug. 27-31, 1995.

- [3] J. Kauraniemi, T. I. Laakso, I. Hartimo, and S. J. Ovaska, "Roundoff noise minimization in a direct form delta operator structure," in *Proc. ICASSP* '96, Vol. 3, pp. 1371 - 1374, Atlanta, GA, May 7-10, 1996.

- [4] K. Premaratne and P. H. Bauer, "Limit cycles and asymptotic stability of delta-operator formulated discrete-time systems implemented in fixed-point arithmetic," in *Proc. ISCAS '94*, Vol. 2, pp. 461-464, London, United Kingdom, May 30 -June 2, 1994.

- [5] J. Kauraniemi and T. I. Laakso, "Elimination of limit cycles in a direct form delta operator filter," in *Proc. EUSIPCO* -96, Vol. 1, pp. 57-60 Trieste, Italy, Sept. 10-13, 1996.

- [6] P. H. Bauer and L.-J. Leclerc, "A computer-aided test for the absence of limit cycles in fixed point digital filters," *IEEE Trans. Signal Processing*, Vol. 39, pp. 2400-2410, Nov. 1991.

- [7] A. I. Abu-El-Haija, "A tight bound on  $\Sigma |h(n)|$  for general second-order H(z)," *IEEE Trans. Circuits Syst.*, Vol. CAS-29, pp. 492-497, July 1982.