# Software Interface for the Configuration of an AD1835A Audio Codec on an ADSP-21369 Processor

Bachelor Thesis

by

**Matthias Hotz**

Graz University of Technology Institute of Broadband Communications

**Head:** Univ.-Prof. Dipl.-Ing. Dr.techn. Gernot Kubin **Advisor:** Dipl.-Ing. Dr.techn. Werner Magnes

# STATUTORY DECLARATION

| I declare that I have authored this thesis independently, that I have not used other than the |

|-----------------------------------------------------------------------------------------------|

| declared sources / resources and that I have explicitly marked all material which has been    |

| quoted either literally or by content from the used sources.                                  |

| Graz, June 28, 2010 |               |

|---------------------|---------------|

|                     | Matthias Hotz |

ABSTRACT Bachelor Thesis

#### Abstract

During the laboratory "Digital Audio Engineering" the configuration of the AD1835A audio codec, itself connected to an ADSP-21369 signal processor, exhibited erratic behavior. The objective of this thesis has been to thoroughly analyze the involved hardware to develop from scratch a reliable, convenient and enhanced software interface for the configuration of the codec. From the physical connections on the printed circuit board over the utilized protocol and the configuration of the communication interface of the processor the entire framework required for the configuration of the codec is discussed in-depth. The process of configuration including all its particular characteristics is investigated and the foundations of the new software interface are exposed. Two exemplary applications, a volume control and an input level meter, depict the practical utilization of the software interface. Concluding, the acquired knowledge is applied to identify the weaknesses and causes of error of the code used during the laboratory.

# Zusammenfassung

Während der Laborübung "Digitale Audiotechnik" zeigte sich der Konfigurationsvorgang für den über den Signalprozessor ADSP-21369 angesprochenen Audio-Codec AD1835A mehrfach als fehlerhaft. Ziel dieser Arbeit war die tiefgründige Analyse der dabei involvierten Hardware, um anschließend von Grund auf eine zuverlässige, komfortable und erweiterte Software-Schnittstelle für die Konfiguration des Codecs zu entwickeln. Es werden von den physikalischen Verbindungen auf der Leiterplatte über das verwendete Protokoll bis zur Konfiguration der Kommunikationsschnittstelle des Signalprozessors alle Voraussetzungen umfassend erörtert, der Vorgang zur Konfiguration des Codecs eingehend analysiert und die grundlegenden Elemente der neu entwickelten Software diskutiert. Abschließend wird die Verwendung der Software-Schnittstelle anhand zweier Anwendungen, einer Lautstärkeregelung und einer Aussteuerungsanzeige, demonstriert und das fundierte Wissen über die Konfiguration für die Analyse des Quellcodes der Laborübung herangezogen, um dessen Fehlerquellen aufzuzeigen.

Bachelor Thesis CONTENTS

# Contents

| 1            | Intr   | roduction                                                  | 1  |

|--------------|--------|------------------------------------------------------------|----|

| <b>2</b>     | Util   | lized Hardware and Objective of the Thesis                 | 1  |

|              | 2.1    | ADSP-21369 Digital Signal Processor                        | 1  |

|              | 2.2    | AD1835A Audio Codec                                        | 2  |

|              | 2.3    | ADSP-21369 EZ-KIT Lite® Evaluation Board                   | 4  |

|              | 2.4    | Objective of the Thesis                                    | 5  |

| 3            | Esse   | ence of the Software Interface                             | 5  |

|              | 3.1    | Connections on the Printed Circuit Board                   | 5  |

|              | 3.2    | Signal Routing                                             | 6  |

|              |        | 3.2.1 Architecture of the Serial Peripheral Interface      | 6  |

|              |        | 3.2.2 Configuration of the Pin Buffers                     | 8  |

|              |        | 3.2.3 Routing Signals between the Pin Buffers and SPI Port | 10 |

|              | 3.3    | SPI Port Configuration on the DSP                          | 10 |

|              |        | 3.3.1 SPI Control Register                                 | 10 |

|              |        | 3.3.2 SPI Baud Rate Register                               | 11 |

|              |        | 3.3.3 SPI Port Flag Register                               | 12 |

|              |        | 3.3.4 Configuration Process                                | 12 |

|              | 3.4    | SPI Communication                                          | 13 |

|              | 3.5    | Representation of the Configuration                        | 15 |

|              | 3.6    | Configuration of the Codec                                 | 17 |

|              | 3.7    | Summary                                                    | 18 |

| 4            | Apr    | plications                                                 | 18 |

| -            | 4.1    | Volume Control                                             | 18 |

|              | 4.2    | Input Level Meter                                          | 20 |

| 5            | Con    | nclusion                                                   | 21 |

| Bi           | ibliog | graphy                                                     | 22 |

| Α.           | ppen   | dix A Excerpts of the AD1835A Data Sheet                   | 23 |

|              |        | Data Frames associated with the Registers                  | 23 |

|              |        | SPI Transfer Diagram                                       | 24 |

| $\mathbf{A}$ | ppen   | dix B Excerpts of the ADSP-21369 Documentation             | 25 |

|              | B.1    | SPI Transfer Diagram                                       | 25 |

|              | B.2    | Clock Relationship to the Input Clock                      | 25 |

| $\mathbf{A}$ | ppen   | dix C Source Code                                          | 25 |

|              | C.1    | Embedding the Software Interface into a Project            | 25 |

|              | C.2    | Signal Routing, SPI Configuration and Communication        | 26 |

|              |        | C.2.1 spi.h                                                | 26 |

|              |        |                                                            | _0 |

|                       | C.2.2 spi.asm                                                                                        | 27 |

|-----------------------|------------------------------------------------------------------------------------------------------|----|

| C.3                   | Codec Configuration Representation and Modification                                                  | 31 |

|                       | C.3.1 ad1835a.h                                                                                      | 31 |

|                       | C.3.2 ad1835a.asm                                                                                    | 37 |

| C.4                   | LED Routing and Control                                                                              | 39 |

|                       | C.4.1 led.h                                                                                          | 39 |

|                       | C.4.2 led.asm                                                                                        | 40 |

| $\operatorname{List}$ | of Figures                                                                                           |    |

| 1                     | ADSP-21369 SHARC® processor block diagram                                                            | 2  |

| 2                     | AD1835A functional block diagram                                                                     | 3  |

| 3                     | ADSP-21369 EZ-KIT Lite $^{\tiny (0)}$ system architecture block diagram $\ \ldots \ \ldots \ \ldots$ | 4  |

| 4                     | Objective of the thesis — from the hardware to the configuration                                     | 5  |

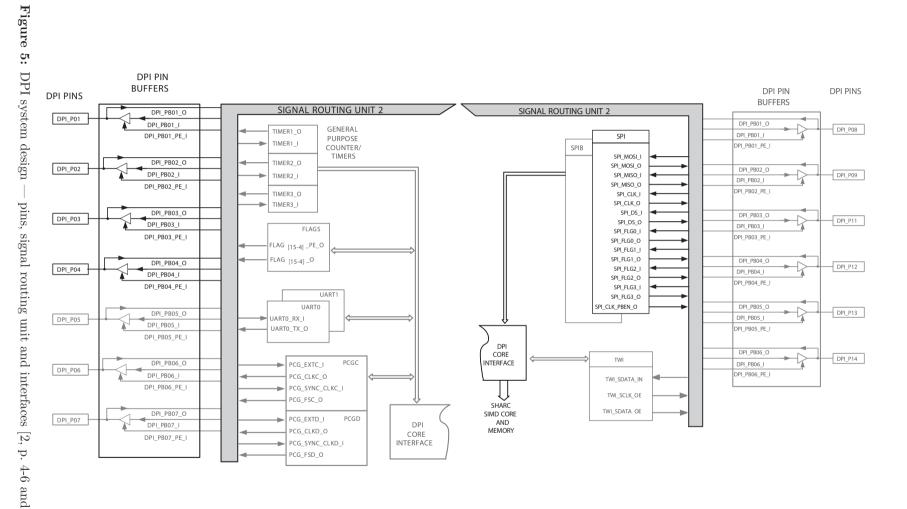

| 5                     | DPI system design — pins, signal routing unit and interfaces                                         | 7  |

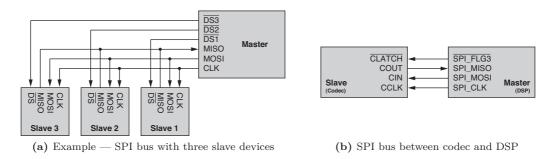

| 6                     | SPI bus architecture                                                                                 | 8  |

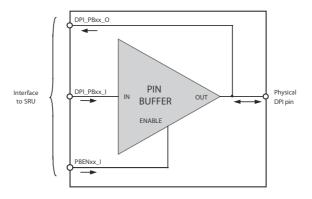

| 7                     | Schematic diagram of the pin buffer                                                                  | 8  |

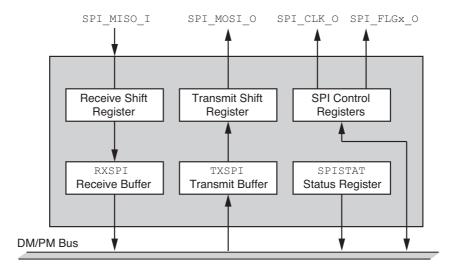

| 8                     | Internal structure of the primary SPI port in core-driven master mode                                | 14 |

| 9                     | Structure of a data frame for configuration                                                          | 16 |

| 10                    | Control register map                                                                                 | 23 |

| 11                    | Data frame: DAC Control 1                                                                            | 23 |

| 12                    | Data frame: DAC Control 2                                                                            | 23 |

| 13                    | Data frame: DAC Volume Control                                                                       | 23 |

| 14                    | Data frame: ADC Peak                                                                                 | 23 |

| 15                    | Data frame: ADC Control 1                                                                            | 24 |

| 16                    | Data frame: ADC Control 2                                                                            | 24 |

| 17                    | Data frame: ADC Control 3                                                                            | 24 |

| 18                    | SPI transfer diagram of the AD1835A control port                                                     | 24 |

| 19                    | SPI transfer diagram for CPHASE = 0                                                                  | 25 |

| 20                    | Clock relationship to the input clock                                                                | 25 |

| List                  | of Tables                                                                                            |    |

| 1                     | Configurable features of the AD1835A codec                                                           | 3  |

| 2                     | Physical connections on the evaluation board                                                         | 6  |

| 3                     | SPI bus signal naming convention                                                                     | 6  |

| 4                     | SPI bus signals of the AD1835A control port                                                          | 8  |

| 5                     | Function table of the pin buffer enable state                                                        | 9  |

| 6                     | Structure of the configuration buffer                                                                | 16 |

Bachelor Thesis LISTINGS

# Listings

| 1  | Syntax of the signal routing macro provided by Analog Devices                         | 9  |

|----|---------------------------------------------------------------------------------------|----|

| 2  | Configuration of the pin buffers                                                      | 9  |

| 3  | Routing of the SPI signals                                                            | 10 |

| 4  | Configuration of the primary SPI port of the DSP $\dots \dots \dots$                  | 13 |

| 5  | Transmission of a data word                                                           | 13 |

| 6  | Waiting for SPI transfer completion                                                   | 14 |

| 7  | Realization of the minimum wait time between successive transfers                     | 15 |

| 8  | Receiving a data word via SPI with transfer initiation mode $TIMOD=01$                | 15 |

| 9  | Transmission of the content of the configuration buffer to the codec                  | 17 |

| 10 | Configuration of the interrupt inputs $\overline{\tt IRQO}$ and $\overline{\tt IRQO}$ | 19 |

| 11 | Interrupt service routine for the push button PB1 $\dots \dots \dots$ .               | 19 |

| 12 | Routing of the LEDs and configuration of the timer                                    | 20 |

| 13 | Interrupt service routine for the timer interrupt                                     | 21 |

Bachelor Thesis 1 INTRODUCTION

# 1 Introduction

The information age brought an omnipresent need for computing power. *Digital signal processors* (DSP) play an important role in satisfying those needs, being the driving force in many devices such as video players, audio devices and mobile phones.

At Graz University of Technology, a laboratory on digital signal processors, "Digital Audio Engineering" (DAL), provides a first insight into this fascinating technology. During the course the processor ADSP-21369 from Analog Devices is studied and put into operation using the associated evaluation board ADSP-21369 EZ-KIT  $Lite^{\oplus}$ . The primary focus of the course is to familiarize the student with the general architecture, arithmetic operations and elements of flow control to subsequently implement some audio applications. Due to the complexity of the hardware its detailed configuration is not considered.

The evaluation board features the audio codec chip AD1835A from Analog Devices which is the bridge between the analog audio signals and the digital world of the DSP. During the course some problems regarding the configuration of the codec chip emerged, occasionally configured settings did not take effect.

This circumstance offered a motivation and an opportunity to dive into the depths of the involved hardware, given the aim for this thesis to rework and expand the configuration of the codec while supplementing the gained knowledge during the course with a deeper understanding of the hardware.

# 2 Utilized Hardware and Objective of the Thesis

The definition of the objective, the configuration of the codec chip AD1835A, may sound rather vague. In order to put it more concretely this chapter provides an introduction to the involved hardware. Starting point is the signal processor, followed by the codec and the evaluation board. Finally, this information is put together to formulate a tangible definition of the established aim.

#### 2.1 ADSP-21369 Digital Signal Processor

The ADSP-21369, in the remainder of this thesis referred to as DSP, is a high performance floating-point processor with a 400 MHz core instruction rate featuring the Super Harvard Architecture ( $SHARC^{\odot}$ ) of Analog Devices which provides a separate program and data memory bus<sup>2</sup>. The DSP possesses a single-instruction, multiple-data (SIMD) computational architecture with two processing elements (PE) supporting 32-bit fixed-point and 32-bit/40-bit floating-point operations. It provides 2 Mbit SRAM and 6 Mbit ROM on-chip memory and has a very rich interface to communicate with peripheral devices including an S/PDIF transceiver, serial ports (SPORT), Universal Asynchronous Receiver Transmitters (UART) and Serial Peripheral Interfaces (SPI) amongst others [5].

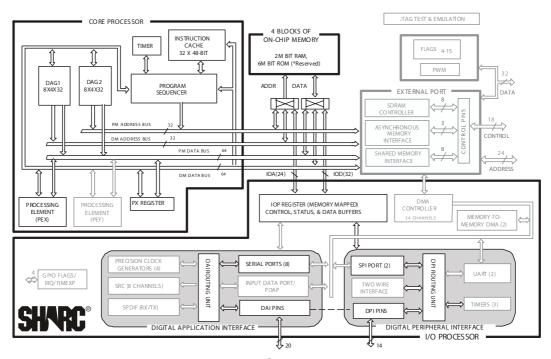

Figure 1<sup>3</sup> depicts a block diagram of the DSP where the relevant parts are displayed in black. By reason of the complexity of this processor only the blocks which are fundamental to the problem at hand are further considered. It is needless to say that the core processor, the on-chip memory and the program and data bus are essential for program execution, but as they covered by the DAL course mentioned in Chapter 1 they are not considered here. Besides the course, continuative information can be found in [5,7,9].

Signal processing applications often need the processor to extensively communicate with offchip devices. To disburden the core processor the ADSP-21369 contains an I/O-processor

$<sup>^{1}\</sup>mathrm{Course}$  number 441.055, taught by DI Dr. Werner Magnes and DI David Fischer.

<sup>&</sup>lt;sup>2</sup>The program memory bus may also be used for data transfers [7, ch. 1].

<sup>&</sup>lt;sup>3</sup>This diagram was taken from a past revision of the programming reference as, in the opinion of the author, it provides a more comprehensive overview than the diagram contained in the current revision.

Figure 1: ADSP-21369 SHARC® processor block diagram [3, p. 1-4]

that handles data transfers to peripherals managing all details of the communication. The I/O processor includes several direct memory access (DMA) channels which enable direct access to the memory without involvement of the core processor. The offered interfaces are divided into two groups named the digital application interface (DAI) and the digital peripheral interface (DPI), each having a specific number of assigned physical pins. These pins are connected to an individual signal routing unit (SRU) for each group which allows a flexible assignment of the physical pins to the interfaces (cf. Figure 1) [9, ch. 2 and 6].

Three serial ports of the DAI are used to receive data from the analog-to-digital converters (ADC) and send data to the digital-to-analog converters (DAC) of the AD1835A audio codec. Anyway, this topic is beyond scope and will not be discussed. More information on the serial ports of the DSP is available in [9, ch. 7].

The configuration of the AD1835A, being the focus of this thesis, is performed using a Serial Peripheral Interface (SPI) port of the DPI. SPI is a bus system that was introduced by Motorola with the MC68HC11 microcontroller. Unfortunately, there is no official SPI standard but, however, the original reference manual of the MC68HC11 might serve as a specification while it is hard to find. The current revision of the manual still contains the chapter on the SPI and is available from Motorola's spin-off Freescale Semiconductors [10, ch. 8]. Before more details about the SPI port and DPI are revealed in Chapter 3, the audio codec and evaluation board are introduced.

#### 2.2 AD1835A Audio Codec

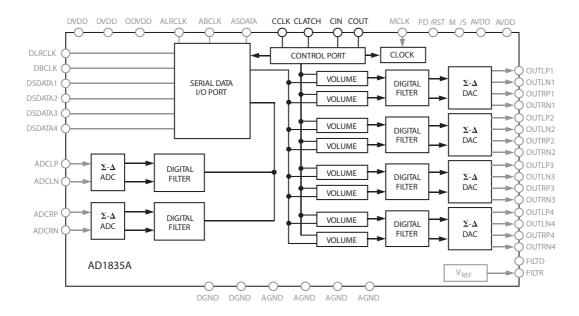

The audio codec chip AD1835A provides a conversion between analog and digital audio signals through one stereo  $\Sigma$ - $\Delta$  ADC and four stereo  $\Sigma$ - $\Delta$  DACs which are accessed via serial ports. The converters can operate at different sample rates and word lengths and many additional features are offered. The key features of this codec chip are summarized in Table 1. All of these features are configurable through a dedicated control port realized as SPI [1].

Figure 2 depicts a functional block diagram of the AD1835A where all blocks affected by

| ADC Features                         | DAC Features                                                      |  |  |

|--------------------------------------|-------------------------------------------------------------------|--|--|

| 16-bit, 20-bit and                   | 24-bit word length                                                |  |  |

| 48 kHz and 96 kHz sample rate        | $48\mathrm{kHz},96\mathrm{kHz}$ and $192\mathrm{kHz}$ sample rate |  |  |

|                                      | (192 kHz: Only one DAC)                                           |  |  |

| Clickless mute f                     | or every channel                                                  |  |  |

| 8 different serial data output modes | 6 different serial data input modes                               |  |  |

| Power-do                             | wn mode                                                           |  |  |

| Optional digital high-pass filter    | Optional de-emphasis filter                                       |  |  |

|                                      | at $32.0\mathrm{kHz},44.1\mathrm{kHz}$ or $48\mathrm{kHz}$        |  |  |

| Peak level information               | 1024-step linear volume control                                   |  |  |

|                                      | for every channel                                                 |  |  |

Table 1: Configurable features of the AD1835A codec

Figure 2: AD1835A functional block diagram [1, p. 1]

the configuration are colored black.

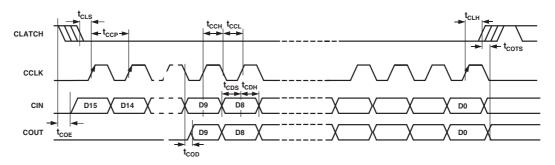

The AD1835A is configured by the content of a set of 10 bit wide control registers, i.e. three registers for DAC related settings, three registers for ADC related settings and eight registers for the DAC output volume settings. Additionally, two 6 bit wide read-only status registers provide information about the peak input level of the left and right ADC if peak readback is enabled. In order to write to a control register or read from a peak level register a 16 bit data word is sent to the codec via the control port. The interface of the control port complies to the SPI specification and consists of four wires, serial clock (CCLK), device select (CLATCH), data input (CIN) and data output (COUT) visible in Figure 2.

Further details about the AD1835A codec regarding its configuration will be introduced in Chapter 3, whereas the next section presents the evaluation board which connects the AD1835A to the DSP.

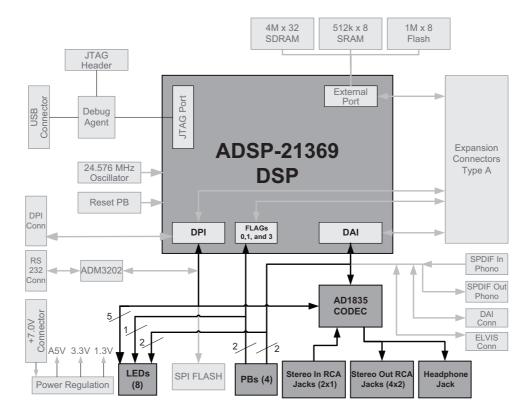

## 2.3 ADSP-21369 EZ-KIT Lite® Evaluation Board

The ADSP-21369 EZ-KIT Lite<sup>®</sup> evaluation board, in the remainder of this thesis named "evaluation board", is a printed circuit board designed to provide a cost-efficient method to evaluate the ADSP-21369 signal processor. Figure 3 depicts a block diagram of its system architecture where the significant blocks are emphasized. The core of the evaluation board is the ADSP-21369 to which different interfaces, connectors and various types of memory are connected to enable a comprehensive assessment of the diverse features of the DSP [6].

Figure 3: ADSP-21369 EZ-KIT Lite® system architecture block diagram [6, p. 2-2]

The audio codec chip AD1835A introduced in Section 2.2 is part of the evaluation board as well. While the serial ports of the codec are connected to the DAI of the DSP, the control port of the codec is connected to the DSP's DPI. Connection to the inputs and outputs of the codec is provided by cinch (RCA) connectors. Additionally, one stereo DAC (DAC 4) is connected to a 3.5 mm TRS connector for use with headphones.

The evaluation board offers eight general-purpose light-emitting diodes (LED) and four general-purpose push buttons connected to the DAI and DPI of the DSP. They will be used in Chapter 4 to demonstrate the capabilities of the configuration routines.

Analog Devices offers a special integrated software development and debugging environment (IDDE) named *VisualDSP++* for software development in C/C++ and assembler for Analog Devices' signal processors<sup>4</sup>. Through the Universal Serial Bus (USB) of the personal computer and the debug agent on the evaluation board, VisualDSP++ is connected to the ADSP-21369 and provides convenient methods to download and test programs on the DSP. Furthermore, libraries and example programs are included [4].

$<sup>^4</sup>$ The ADSP-21369 EZ-KIT Lite $^{\otimes}$  includes an evaluation suite of VisualDSP++.

# 2.4 Objective of the Thesis

Chapter 1 mentioned that the code<sup>5</sup> used to configure the AD1835A codec during the DAL course frequently caused problems by means of settings not taking effect. This erratic behavior was best noticed when DAC volumes were changed.

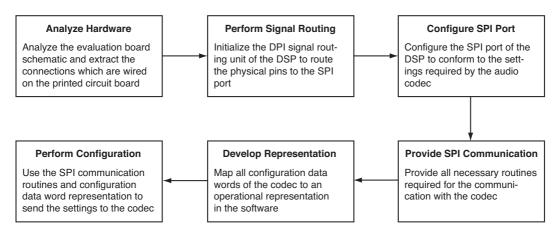

The objective of this thesis was to rebuild the whole software from scratch which is involved in the configuration of the AD1835A codec, i.e. all software required to alter any setting of the codec including the necessary communication framework. Based on the information about the hardware previously communicated in this chapter, the goal can be concretized as illustrated in Figure 4.

Figure 4: Objective of the thesis — from the hardware to the configuration

# 3 Essence of the Software Interface

The hardware overview of Chapter 2 was utilized to concretize the goal, yielding the road map for the process towards an implementation of the software interface depicted in Figure 4. In this chapter the implementation of the software interface for the configuration of the AD1835A codec will be discussed, following the aforementioned road map.

The implementation will be done using the assembler language of the DSP, being predestined and illustrative for this task since it is tied very closely to the hardware of the DSP. However, a description of the assembler language would be beyond scope of this thesis. More information about the instruction set of the ADSP-21369 is available in [7, ch. 9-11], programming in assembler using VisualDSP++ is described in [8].

#### 3.1 Connections on the Printed Circuit Board

As it was mentioned in Chapter 2 the physical pins of the DSP are not connected directly to its internal SPI port. Instead, the physical pins are connected to a signal routing unit (SRU) that can be configured to route the signals between the physical pins and the internal interfaces, e.g. an SPI port. In order to perform the routing the physical pins of the DSP which are connected to the control port of the AD1835A have to be determined.

The schematic of the evaluation board is available in [6, app. B]. The AD1835A audio codec chip (U31) is shown on sheet 5 of the schematic. By tracing the signal labels of the AD1835A's pins CIN, COUT, CCLK and CLATCH<sup>6</sup> to the ADSP-21369 (U44) on sheet 2 of the schematic, the physical pins of the DSP are investigated. Using the pin assignment table from the DSP's

<sup>&</sup>lt;sup>5</sup>This code was extracted from one of Analog Devices' example programs included with VisualDSP++. <sup>6</sup>CLATCH is connected through switch SW15 which is assumed to be in its on-position.

data sheet [5, p. 51] the names of the pins in Analog Devices' software library are uncovered. These observations are summarized in Table 2.

| Signal of Physical pin<br>AD1835A at ADSP-2136 |     | Pin's name in software library |  |  |

|------------------------------------------------|-----|--------------------------------|--|--|

| CIN                                            | B15 | DPI_P01                        |  |  |

| COUT                                           | A16 | DPI_P02                        |  |  |

| CCLK                                           | A15 | DPI_P03                        |  |  |

| CLATCH                                         | B14 | DPI_P04                        |  |  |

**Table 2:** Physical connections on the evaluation board

## 3.2 Signal Routing

The overview of the hardware in Chapter 2 revealed that the AD1835A codec offers an SPI port, i.e. the control port for its configuration. The DSP contains two SPI ports, entitled primary (SPI) and secondary (SPIB) SPI port, whereas the *primary SPI port* is used for communication with the codec. The SPI ports are connected to the signal routing unit of the DPI, named SRU2, as depicted in Figure 5<sup>7</sup>.

In order to enable the configuration of the AD1835A, the control port of the codec, wired to the DPI pins of the DSP, and the primary SPI port of the DSP need to be connected through the SRU. Routing a physical DPI pin to a "virtual" pin of the primary SPI port by means of the SRU requires the

- configuration of the pin buffer of the physical pin and

- routing of the internal pin buffer connectors to the virtual pin of the SPI port.

These steps depend on architectural information about the SPI. Therefore, the architecture of the SPI is discussed beforehand, followed by the configuration of the pin buffers and the routing to the primary SPI port.

#### 3.2.1 Architecture of the Serial Peripheral Interface

The SPI is a bus system<sup>8</sup> enabling serial data transfer between a master and one or more slave devices. The master controls and initiates all transfers, whereas the addressed slave device, chosen via a dedicated select signal, only responds to the master. The physical connection between the master and slave devices consists of four wires specified in Table 3. Figure 6a illustrates the wiring of an SPI bus consisting of a master and three slave devices.

| Signal      | Full name                     |

|-------------|-------------------------------|

| SCLK or CLK | (Serial) Clock                |

| MOSI        | Master Output, Slave Input    |

| MISO        | Master Input, Slave Output    |

| SS or DS    | Slave Select or Device Select |

**Table 3:** SPI bus signal naming convention

<sup>&</sup>lt;sup>7</sup>This diagram was taken from a past revision of the hardware reference as, in the opinion of the author, it provides a more comprehensive overview than the depictions contained in the current revision.

<sup>&</sup>lt;sup>8</sup>Only the typical SPI bus wiring is considered since "daisy-chaining" of slave devices is not relevant here.

4-7]

| Control port signal name | Conventional signal name | Description         |

|--------------------------|--------------------------|---------------------|

| CCLK                     | CLK                      | Clock Input         |

| CIN                      | MOSI                     | Slave Input         |

| COUT                     | MISO                     | Slave Output        |

| CLATCH                   | DS                       | Device Select Input |

Table 4: SPI bus signals of the AD1835A control port

Figure 6: SPI bus architecture

At the SPI bus for the configuration of the codec, the DSP acts as master and the AD1835A is a slave<sup>9</sup>. The SPI port of the DSP mostly follows the naming convention of Table 3, except the four available the slave select outputs are named "flag" [9, p 12-3]. The control port of the codec, however, uses completely different names. Based on the information from the data sheet of the AD1835A [1, p. 12], the correspondence to the conventional signal names is established in Table 4. Figure 6b summarizes the determined SPI bus connections.

#### 3.2.2 Configuration of the Pin Buffers

Before the information about the bus architecture is utilized, another concept needs to be introduced. Within the context of the SRU a physical DPI pin is replaced by a logical interface named *pin buffer*. Its internal interface to the SRU consists of three connectors, enable (PBENxx\_I), input (DPI\_PBxx\_I) and output (DPI\_PBxx\_0), as depicted in Figure 7. Depending

Figure 7: Schematic diagram of the pin buffer [9, p. 6-8]

$<sup>^9{</sup>m The}$  SPI flash memory shown in Figure 3 is also connected to this SPI bus as slave device. This was neglected to avoid unnecessary complexity.

on the logic level at the enable connector, the physical pin acts as input or output as shown in Table 5. It might be confusing that, for example, the output <code>DPI\_PBxx\_O</code> yields the state of the physical pin if it is configured as input. This naming convention becomes clear when the flow of information in reference to the pin buffer is considered; the pin buffer outputs the state of the physical pin to the SRU.

| Pin enable (PBENxx_I) | Physical pin function | Active pin buffer connector |

|-----------------------|-----------------------|-----------------------------|

| HIGH                  | Output                | DPI_PBxx_I                  |

| LOW                   | Input                 | DPI_PBxx_O                  |

Table 5: Function table of the pin buffer enable state

This simplified description of pin buffers, where its mode of operation is "hard-wired", is sufficient for the problem at hand. More information on the function of the pin buffers, e.g. how to use the the output signal of an interface to control the enable signal of a pin buffer, is available in [9, ch. 6].

The principle behind the configuration of the SRU, and this includes the pin buffers, is that each output has an assigned identifier and every input a dedicated configuration register <sup>10</sup>. In order to connect an output to an input, the identifier of the output has to be written to the configuration register of the input. This task is supported by the macro SRU provided by Analog Devices with VisualDSP++ in SRU.H [9, p. 6-42 ff.].

Listing 1: Syntax of the signal routing macro provided by Analog Devices

```

SRU(Output_Signal, Input_Signal);

```

The signal names follow the naming convention

## PERIPHERAL\_FUNCTION\_DIRECTION

where e.g. "peripheral" is SPI, "function" is CLK and "direction" is 0 for output [9, p. 6-7]. Finally, the information gathered since the beginning of this chapter is combined. Table 2

specifies which physical pins of the DAI need to be configured and Figure 6b shows the direction of data flow for each pin. Considering the naming convention for pin buffers visible in Figure 7 and the function of the enable signal depicted in Table 5, the code to configure the pin buffers using the SRU-macro from above can be derived.

Listing 2: Configuration of the pin buffers

```

1 // DPI_P01: Output (MOSI)

2 SRU(HIGH, DPI_PBEN01_I);

3

4 // DPI_P02: Input (MISO)

5 SRU(LOW, DPI_PBEN02_I);

6

7 // DPI_P03: Output (Clock)

8 SRU(HIGH, DPI_PBEN03_I);

9

10 // DPI_P04: Output (Device select for AD1835A)

11 SRU(HIGH, DPI_PBEN04_I);

```

<sup>&</sup>lt;sup>10</sup>Additionally, the inputs and outputs are arranged in groups [9, p. 6-16 ff.]. This will not be considered to avoid unnecessary complexity.

#### 3.2.3 Routing Signals between the Pin Buffers and SPI Port

Figure 5 illustrates that by configuring the pin buffers the physical pin is made available to the "core" of the signal routing unit. All that is left to connect the control port of the codec to the DSP is to route the signals from the pin buffers to the primary SPI port of the DPI. The involved signals of the SPI port of the DSP are depicted in Figure 6b. Using the information on pin buffers and the SRU-macro from the previous section, the code to route the signals can be composed.

Listing 3: Routing of the SPI signals

#### 3.3 SPI Port Configuration on the DSP

Previously the connection between the DSP's primary SPI port and the codec's control port was established. In addition to the bus architecture the SPI specification defines three attributes for a connection, the clock rate, word length and mode. Therefore, the SPI port of the DSP needs to be configured to conform to the settings required by the codec. Additionally, some DSP–related settings of the SPI port have to be set. The complete configuration of the primary SPI port is described by the content of three registers, the SPI control register, SPI band rate register and SPI port flag register. In the following the settings provided by these registers are disussed and eventually the code for the configuration is presented.

#### 3.3.1 SPI Control Register

The main part of the configuration of the primary SPI port is accessible through the SPI control register SPICTL [9, p. A-140 ff.]. It consists of 18 different settings why only the essential ones are discussed.

Each setting of the register has a short name. Along with VisualDSP++ Analog Devices provides an ADSP-21369 specific header file def21369.h that defines constants of the same name to be used for configuration. These short names will be introduced along with the description of each setting for the code at the end of the section.

SPI Port Enable If the bit SPIEN is set, the SPI port is enabled, otherwise disabled.

**SPI Master Select** As mentioned in Section 3.2.1 the DSP has to act as master on the SPI bus. Setting the SPIMS bit configures the primary SPI port as master.

Word Length In order to modify the content of a control register of the codec a 16 bit data word has to be sent to its control port as described in Section 2.2. Therefore, the 2 bit wide SPI bus word length code WL in SPICTL has to be set to WL16, specifying 16 bit word length.

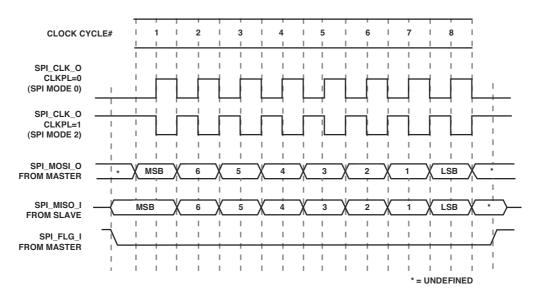

Clock Polarity and Clock Phase The SPI specification defines four modes by means of the two-valued settings *clock polarity* and *clock phase*. The clock polarity specifies whether the clock signal is active-low or active-high and the clock phase defines when the data is put on the bus. Figure 19 in Appendix B provides the SPI transfer diagram for clock phase CPHASE = 0 and clock polarity CLKPL = 0 and CLKPL = 1. By comparision with the SPI transfer diagram of the AD1835A depicted in Figure 18 in Appendix A, the SPICTL settings CLKPL = 0 and CPHASE = 0 corresponding to SPI mode 0 are investigated 11. Thus, both bits, CLKPL and CPHASE, are *not* set.

Most Significant Byte First The setting MSBF specifies if the most significant byte of the data word is sent first. Figure 18 in Appendix A depicts that the control port of the codec assumes that the byte order is big-endian, thus this bit has to be set.

Transfer Initiation Mode Basically there are two alternatives to manage the SPI communication, direct memory access (DMA) provided by the I/O processor and core driven operation. As the configuration of the codec only requires the occasional transfer of a handful of data words, DMA is not purposeful due to the additional configuration overhead and negligible unloading of the core processor because of the small amount of transmitted data. Therefore, core driven operation is used and DMA is not discussed further.

The transfer initiation mode setting TIMOD consists of two bits, whereas the more significant bit selects between DMA (TIMOD2) and core driven (0) operation and the second bit defines how a transfer is initiated in the core driven mode, by a request to send (TIMOD1) or receive (0) a data word<sup>12</sup>. The control registers of the codec are modified by sending data words to its control port, therefore, the TIMOD1 mode is suited best for this task.

#### 3.3.2 SPI Baud Rate Register

The SPI baud rate register SPIBAUD configures the clock rate of the SPI bus [9, p. A-148]. The bits 15-1 of SPIBAUD are named BAUDR and specify the divisor by which the SPI baud rate  $f_{\text{SPI}}$  is related to the peripheral clock rate  $f_{\text{PCLK}}$  of the I/O processor. In master mode this relation is given by Equation (1) [9, p. 12-6].

$$f_{\text{SPI}} = \frac{f_{\text{PCLK}}}{8 \cdot \text{BAUDR}} \tag{1}$$

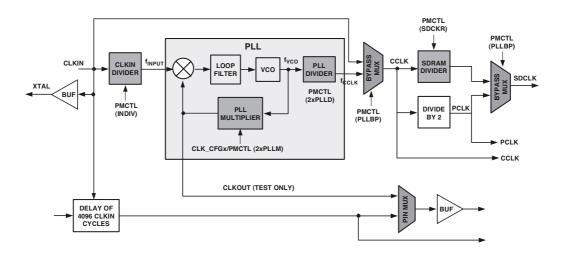

In order to determine BAUDR for a specific SPI baud rate  $f_{PCLK}$  needs to be known. The peripheral clock rate  $f_{PCLK}$  is half the core clock rate  $f_{CCLK}$ , whereas the core clock is the output of the phase-locked loop (PLL) (cf. Figure 20 in Appendix B).

$$f_{\rm PCLK} = \frac{f_{\rm CCLK}}{2} \tag{2}$$

The PLL is controlled via the power management control register PMCTL where INDIV configures the input pre divider, PLLM the multiplier and PLLD the post divider [9, ch. 16]. The details of the PLL configuration are beyond scope, thus only the necessary setting values for the calculation of  $f_{\rm CCLK}$  are considered. However, the PLL is configured with PLLM = 27, PLLD = 2 and INDIV = 0 which deactivates input pre divisor. The input clock rate  $f_{\rm CLKIN}$  of the DSP is 24.576 MHz as shown on sheet 2 of the evaluation board schematic [6, app. B]. Utilizing this information and applying the equation for the core clock rate given in [5, p. 19] (with  $f_{\rm CLKIN} = f_{\rm INPUT}$ ) yields  $f_{\rm CCLK}$  as depicted in Equation (3).

$$f_{\text{CCLK}} = f_{\text{CLKIN}} \cdot \frac{\text{PLLM}}{\text{PLLD}} = 24.576 \,\text{MHz} \cdot \frac{27}{2} = 331.776 \,\text{MHz}$$

(3)

<sup>&</sup>lt;sup>11</sup>More information about the SPI transfer modes is found in [10, ch. 8] and [9, ch. 12].

<sup>&</sup>lt;sup>12</sup>Details on how the sending or receiving of a data word is requested is discussed in Section 3.4.

By substituting Eq. (2) in Eq. (1), BAUDR can be expressed in dependence of  $f_{SPI}$  and  $f_{CCLK}$ . Considering that  $f_{SPI}$  specifies an upper limit for the SPI baud rate the relation in Equation (4) is derived.

$$f_{\rm SPI} > \frac{f_{\rm PCLK}}{8 \cdot {\rm BAUDR}} = \frac{f_{\rm CCLK}}{16 \cdot {\rm BAUDR}} \qquad \Rightarrow \qquad {\rm BAUDR} > \frac{f_{\rm CCLK}}{16 \cdot f_{\rm SPI}} \tag{4}$$

In the data sheet of the AD1835A a maximum serial bit clock frequency ( $\rightarrow f_{SPI}$ ) of 12.5 MHz is specified for the control port [1, p. 13]. With Eq. (3) and Eq. (4) the valid range of values for BAUDR is determined.

$$\mathsf{BAUDR} > \frac{f_{\mathsf{CCLK}}}{16 \cdot f_{\mathsf{SPI}}} = \frac{331.776\,\mathrm{MHz}}{16 \cdot 12.5\,\mathrm{MHz}} = 1.66 \qquad \Rightarrow \qquad \mathsf{BAUDR} \ge 2 \tag{5}$$

An additional "safety margin" is added and the value  $(4)_{\rm dec} = (4)_{\rm hex}$  is chosen for BAUDR. Considering that BAUDR begins at bit 1, the value  $(8)_{\rm hex}$  is written to SPIBAUD.

#### 3.3.3 SPI Port Flag Register

In Section 3.2.1 it was already mentioned that the device select signals are called "flags" in the context of the DSP's SPI port. The flags of the primary SPI port are controlled by the SPI port flag register SPIFLG, where each of the four flags has an assigned device select enable (DSOEN - DS3EN) and device select control bit (SPIFLG0 - SPIFLG3) [9, p. A-150 f.]. Therefore, e.g. to enable the SPI port signal SPI\_FLG3\_0 (cf. Figure 5), i.e. the device select output "flag 3", the bit DS3EN in SPIFLG has to be set. The state of this device select signal is then controlled by the bit SPIFLG3. Considering that the device select signal is active low, the slave is selected when the SPIFLG3 bit is cleared.

If CPHASE = 0 in SPICTL, which is the case in this configuration, all enabled device select signals are controlled by the internal SPI hardware of the DSP. If a SPI transfer is initiated, independent of the SPIFLGx bit all enabled device select signals are pulled low for the duration of the transfer [9, p. 12-15 ff.].

Figure 6b depicts that flag 3 is used as device select signal for the AD1835A codec, consequently, DS3EN needs to be set in SPIFLG. Additionally, for the sake of formality all SPIFLGx bits are set to achieve a save initial state.

#### 3.3.4 Configuration Process

Figure 1 shows that the registers of the I/O processor are memory-mapped, thus the previously discussed SPI port configuration registers are accessed via the data memory bus. Before performing the configuration it has to be considered that the SPI configuration may only be changed safely when some preconditions are fulfilled [9, p. 12-22].

- 1. There must not be any data transfer active.

- 2. No slaves may be selected.

- 3. The SPI port is disabled.

The means to check if a transfer is active and block execution until its completion are presented in Section 3.4 and, therefore, it is only noted in the code shown below. How the other prerequisites are accomplished was already implicitly mentioned. The device select signals are disabled by clearing the DSXEN bits in SPIFLG and the SPI port is disabled by clearing the SPIEN bit in SPICTL<sup>13</sup>. The code of the complete configuration incorporating all

$<sup>^{13}</sup>$ When the SPI port is disabled the transmit and receive buffer is cleared, leading to a defined basis for subsequent transfers.

discussed settings and aspects of the execution sequence is listed below. Attention should be paid to the modification of the SPI control register, enabling and disabling the SPI port has to be separated from changing other settings in SPICTL.

Listing 4: Configuration of the primary SPI port of the DSP

```

1 // Wait for active data transfer to finish

2 //

--> Discussed in the next section

4 // Disable SPI port: Clear SPIEN bit

_{5} r0 = dm(SPICTL);

_6 r1 = \simSPIEN;

_{7} r0 = r0 and r1;

s dm(SPICTL) = r0;

10 // Set the SPI baud rate

11 \text{ r0} = 0x8;

_{12} dm(SPIBAUD) = r0;

14 // Disable all slave select lines (Clear DSxEN and set SPIFLGx)

r0 = SPIFLG0 | SPIFLG1 | SPIFLG2 | SPIFLG3;

dm(SPIFLG) = r0;

17

18 // Configure the primary SPI port

19 r0 = TIMOD1 | // Trigger transfer by write request

WL16 | // 16 bit word length

MSBF

| // Send most significant byte first

21

SPIMS; // Set to SPI master

23 \text{ dm}(SPICTL) = r0;

25 // Enable the device select signal for the AD1835A

26 r0 = DS3EN | SPIFLG0 | SPIFLG1 | SPIFLG2 | SPIFLG3;

27 \text{ dm}(SPIFLG) = r0;

29 // Enable the SPI port: Set SPIEN bit

_{30} r0 = dm(SPICTL);

_{31} r1 = SPIEN;

_{32} r0 = r0 or r1;

33 \text{ dm}(SPICTL) = r0;

```

#### 3.4 SPI Communication

The SPI port is routed, configured and, consequently, ready for data transfers. In order to initiate a transfer, an insight into the internal structure of the SPI port is necessary.

The primary SPI port contains a transmit and a receive *shift register* which are *not* directly accessible. These registers serially transmit, respectively receive data synchronously with the SPI clock signal. A shift register is written, respectively read by the associated *transmit data buffer* TXSPI and *receive data buffer* RXSPI via the data memory bus as depicted in Figure 8.

In Section 3.3 the transfer initiation mode was set to TIMOD = 01, defining core-driven operation of the SPI port whereas a transfer is initiated by the request to send a data word. A request to send a data word is deposited by simply writing the data word into the transmit data buffer TXSPI.

**Listing 5:** Transmission of a data word

```

// Example: Transmit the data word 0x1234

2 r0 = 0x1234;

3 dm(TXSPI) = r0;

```

Figure 8: Internal structure of the primary SPI port in core-driven master mode

In core-driven SPI transfers, if a data word is written to TXSPI when another data transfer is already active, the current buffer content is overwritten and the new data word is transferred, leading to the corruption of the preceding data word. Therefore, a transmission may only be initiated if no other transfer is active.

Information about the status of the primary SPI port is available through the read-only SPI port status register SPISTAT [9, p. A-148 ff.]. Two bits thereof indicate the transmit transfer status.

- TXS describes the TXSPI buffer status. This bit is set if the buffer is full and cleared if the buffer is empty, i.e. it was emptied into the transmit shift register.

- SPIF describes the state of the transfer. This bit is cleared if a transfer is active, i.e. data is shifted out of the transmit shift register<sup>14</sup>, and set if the transfer is finished, i.e. the transmit shift register is empty<sup>14</sup>.

In order to assure that no transfer is active, TXS needs to be cleared and subsequently SPIF to be set [9, p. 12-36 f.]. The program execution is blocked by subsequently polling these flags until no transfer is active anymore<sup>15</sup>.

Listing 6: Waiting for SPI transfer completion

```

// Wait for the TXS bit to be cleared

// => Transmit data buffer was emptied

testTXS:

// ustat1 = dm(SPISTAT);

bit tst ustat1 TXS;

if TF jump testTXS;

// wait for the SPIF bit to be set

// => Transmit shift register was emptied

testSPIF:

// ustat1 = dm(SPISTAT);

bit tst ustat1 SPIF;

if not TF jump testSPIF;

```

$<sup>^{14}</sup>$ Assuming that the transfer initiation mode is set to TIMOD = 01.

$<sup>^{15}</sup>$ The loops for polling were implementing using the JUMP instruction as the DO/UNTIL instruction does not support bottom—controlled loops [7, p. 9-55].

Commonly, SPI slave devices require that a minimum wait time between successive word transfers is maintained. Unfortunately, this is not specified in the data sheet of the AD1835A. An indication for the magnitude of the wait time is given by the frame delay required by the DSP's SPI port if it is configured as a slave device, which is specified with 2 SPI clock periods  $T_{\text{SPI}}$  [9, p. 12-16]. On the basis of this specification, it is assumed that 4 SPI clock periods are a sufficient wait time for the control port of the AD1835A codec.

This minimum wait time is achieved by a loop of no-operation instructions (NOP), whereas each NOP takes one core clock cycle to execute. The number of core clock cycles to establish the required wait time is determined by the ratio of the core clock rate  $f_{\text{CCLK}}$  and the SPI clock rate  $f_{\text{SPI}}$ . In conjunction with Eq. (1) and Eq. (2) from Section 3.3, the number  $N_{\text{CCLK}}$  of required core clock cycles is derived as shown in Equation (6), whereas  $T = \frac{1}{f}$  denotes the periodic time of the respective clock signal.

$$\begin{split} N_{\text{CCLK}} &= \frac{2 \cdot T_{\text{SPI}}}{T_{\text{CCLK}}} = \frac{2 \cdot f_{\text{CCLK}}}{f_{\text{SPI}}} = \frac{4 \cdot f_{\text{PCLK}}}{f_{\text{SPI}}} = \frac{32 \cdot \text{BAUDR} \cdot f_{\text{SPI}}}{f_{\text{SPI}}} = \\ &= 32 \cdot \text{BAUDR} = 32 \cdot 4 = 128 \end{split} \tag{6}$$

Consequently, the wait time between successive SPI data word transmissions is realized with the code shown below.

Listing 7: Realization of the minimum wait time between successive transfers

```

// Wait minimum wait time between successive transfers

2 lcntr = 128, do waitTimeLoop until LCE;

3 waitTimeLoop: nop;

```

These are all means required for the successive transmission of data words. Additionally, the transmission of a data word may also be used to receive a data word. Every time a data word is transmitted, the data is sent through the ("virtual") SPI\_MOSI pin of the SPI port. Synchronously, the data from the SPI\_MISO pin is shifted into the receive shift register of the SPI port. Therefore, every time a data word is transmitted, simultaneously a data word is received. Analog to the TXS bit, the RXS bit in the SPI port status register SPISTAT indicates when the receive buffer is full. In order to read the data word that was received synchonously to the transmission of a data word on the primary SPI port, the RXS is polled until it is set and afterwards the data word is read from the receive buffer RXSPI.

Listing 8: Receiving a data word via SPI with transfer initiation mode TIMOD = 01

```

// Here: Transmit data word and wait for transfer completion

// Wait for the RXS bit to be set

// => Receive data buffer is full

testRXS:

ustat1 = dm(SPISTAT);

bit tst ustat1 RXS;

if not TF jump testRXS;

// Read the data word from the primary SPI port receive data buffer r0 = dm(RXSPI);

```

## 3.5 Representation of the Configuration

The communication channel to the control port of the AD1835A via the SPI is established. For a convenient modification of the configuration of the codec some kind of representation thereof is necessary. The approach taken is to keep a mirrored version of the codec's configuration in the internal memory of the DSP.

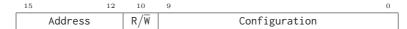

As mentioned in Section 2.2, a control register of the codec is modified by sending a specific

data frame to the codec's control port. The basic structure of such a data frame is shown in Figure 9. The four most significant bits contain the address of the target register, followed by one bit declaring the type of operation (read or write). The ten remaining bits specify the configuration which should be set, or, if a read operation is performed, they are ignored. The exact composition of all data frames is available in Appendix A.

Figure 9: Structure of a data frame for configuration

Instead of only storing the control register content in the memory of the DSP, a buffer labeled \_ad1835a\_config\_buffer is created in the data segment which contains a data word for each data frame. The assignment of the data words of this configuration buffer to the respective data frame is depicted in Table 6, where the offset from the base address of the buffer is shown as well<sup>16</sup>. Therefore, if a setting is changed in the configuration buffer, the associated data frame is instantly available through the related data word and can be sent to the codec.

| Number Offset from base address |    | Associated control register |  |

|---------------------------------|----|-----------------------------|--|

| 1                               | 0  | DAC Control 1               |  |

| 2                               | 1  | DAC Control 2               |  |

| 3                               | 2  | DAC Volume-Left 1           |  |

| 4                               | 3  | DAC Volume-Right 1          |  |

| 5                               | 4  | DAC Volume-Left 2           |  |

| 6                               | 5  | DAC Volume-Right 2          |  |

| 7                               | 6  | DAC Volume-Left 3           |  |

| 8                               | 7  | DAC Volume-Right 3          |  |

| 9                               | 8  | DAC Volume-Left 4           |  |

| 10                              | 9  | DAC Volume-Right 4          |  |

| 11                              | 10 | ADC Control 1               |  |

| 12                              | 11 | ADC Control 2               |  |

| 13                              | 12 | ADC Control 3               |  |

Table 6: Structure of the configuration buffer

The configuration buffer is initialized by setting the address-,  $R/\overline{W}$ - and configuration-field of each data word as depicted in Figure 9. The settings of the AD1835A codec are concisely described in [1, p. 18] and a replication thereof is probably not worthwhile. However, in the following some remarks will be given.

After a basic configuration is sent to the codec, access to its configuration is probably mostly necessary to use the mute, volume, peak level information and maybe the power-down feature. The DAC Control 2 and ADC Control 2 register enable the individual muting of every DAC output and ADC input, whereas the eight DAC Volume Control registers provide an individual volume control for every DAC output which will be utilized in Chapter 4. Further, the AD1835A codec provides information about the peak input level of each ADC via the two ADC Peak registers if peak readback is enabled in ADC Control 3. The ADC Peak registers are somewhat special, as they are the only registers which are read. This is the reason, why they do not appear in Table 6. How these registers are read will be discussed in Section 3.6, whereas Chapter 4 presents an example of use.

In DAC Control 1 and ADC Control 2 the data format and word length for the serial ports for the DAC and ADC data of the codec is configured. It should be kept in mind that these

<sup>&</sup>lt;sup>16</sup>The data memory is addressed in 32-bit words. More information is available in [7, ch. 7].

settings have to conform to the settings of the DSP's serial ports and, therefore, may not be changed without further consideration.

### 3.6 Configuration of the Codec

Section 3.5 introduced the configuration buffer, which contains the data frames with the desired configuration of the codec. In order to apply the configuration, these data frames are sent to the codec's control port by the means derived in Section 3.4.

This is accomplished by iterating through all data frames in the configuration buffer using a data address generator (DAG) [7, ch. 6] of the processor, whereas each data frame is synchronously sent and the minimum wait time between successive transfers is maintained.

- 1. Initiate the transmission by writing the data word into the transmit data buffer TXSPI.

- 2. Wait for the transfer to finish by polling the TXS and SPIF status bit.

- 3. Maintain the minimum wait time using a loop of NOP instructions.

Considering the configuration buffer name \_ad1835a\_config\_buffer and the code fragments from Section 3.4, the code to send the configuration can be formulated as shown below. Individual data frames are sent similarly by only using the code from the loop body.

Listing 9: Transmission of the content of the configuration buffer to the codec

```

_{

m 1} // Use the index and modify register 0 of DAG1 for buffer access

2 i0 = _ad1835a_config_buffer; // Base address of the buffer

3 m0 = 1;

// Increment address in steps of 1

_{5} // Loop through all data frames and send them to the AD1835A

6 lcntr = @_ad1835a_config_buffer, do sendCalibrationBufferLoop until LCE;

// Read and transmit a data frame

r0 = dm(i0, m0);

9

dm(TXSPI) = r0;

10

11

// Wait for the TXS bit to be cleared

testTXS:

13

ustat1 = dm(SPISTAT);

bit tst ustat1 TXS;

15

if TF jump testTXS;

16

17

// Wait for the SPIF bit to be set

18

testSPIF:

19

ustat1 = dm(SPISTAT);

20

bit tst ustat1 SPIF;

21

if not TF jump testSPIF;

22

// Wait minimum wait time between successive transfers

lcntr = 128, do waitTimeLoop until LCE;

25

waitTimeLoop: nop;

26

27

28 sendCalibrationBufferLoop: nop;

```

The considerations and the code presented at the end of Section 3.4 is used to read the content of an ADC Peak register<sup>17</sup>. The sequence of actions required to achieve the reading of a peak register with the transfer initation mode configured in Section 3.3 is as follows.

<sup>&</sup>lt;sup>17</sup>Assuming that peak readback is enabled in ADC Control 3.

- 1. Send a data frame to the codec which contains the address of the desired ADC Peak register in the address-field and where the  $R/\overline{W}$  bit set. The configuration field of the data frame is ignored. Thereupon the codec transfers the value of the addressed peak register into its transmit shift register and resets the peak register for a new peak level determination.

- 2. Send a dummy data frame, e.g. an arbitrary data frame from the configuration buffer, to the codec to shift the data from the codec's transmit shift register into the receive shift register of the primary SPI port of the DSP.

- 3. Poll the RXS status bit until it is set and, therefore, the receive data buffer is full.

- 4. Read the receive data buffer RXSPI to obtain the peak value.

As the clue of reading the peak registers lies in the sequence of the individual steps but does not introduce any new aspects regarding the code, no listing is included.

# 3.7 Summary

This chapter described the fundamental steps required to configure an AD1835A codec chip on an ADSP-21369 signal processor brought together via an ADSP-21369 EZ-KIT Lite<sup>®</sup> evaluation board and illustrated the principles of the involved hardware. Starting from the connections on the printed circuit board, the signals of the control port of the codec were traced to the DPI of the DSP and routed to the DSP's primary SPI port by programming the SRU. The SPI port was configured to comply to the requirements of the codec and the means for communication were established, incorporating the issues which evolve when successive transfers are performed. Subsequently, a representation of the codec's configuration was introduced to finally carry out the configuration, bringing together all developed components.

The actual software interface uses the knowledge presented above as building blocks for a set of constants, macros and subroutines to provide convenient means to alter the configuration of the codec and read the content of its peak level registers. In Appendix C the essential source code is listed and its integration is explained. A detailed discussion of the internal structure of the software interface would go beyond the scope, however, with the information in this chapter its functionality should be comprehensible.

# 4 Applications

Chapter 3 discussed the configuration of the AD1835A codec using the primary SPI port of the DSP in-depth. The chapter concluded with the introduction of the software interface presented in Appendix C which provides convenient means to configure the codec. This chapter concisely demonstrates two examples of use to illustrate the practical aspect of the configuration as well.

The starting point for these examples is the project "Talkthrough" provided in the DAL course referred to in Chapter 1. That code in turn is derived from the project "Talkthru Analog In-Out (ASM)" provided by Analog Devices with VisualDSP++ included in the ADSP-21369 EZ-KIT Lite<sup>®</sup>.

#### 4.1 Volume Control

The evaluation board offers four general-purpose push buttons, whereas the push buttons PB1 and PB2 are connected to the flag-pins FLAG1 and FLAG0 of the DSP which can be configured as interrupt inputs  $\overline{\text{IRQ1}}$  and  $\overline{\text{IRQ0}}$  [6, p. 1-12], [9, p. 17-27 ff.], [7, p. 4-29 ff.]. These two push buttons are utilized to realize a linear volume control. The output volume of all DACs

Bachelor Thesis 4 APPLICATIONS

is increased (PB1) and decreased (PB2) by modifying the DAC Volume Control registers of the codec using the software interface discussed in Chaper 3. Therefore, the interrupt vector table (IVT) is supplemented with two additional interrupt service routines (ISR) [7, app. C], \_push\_button\_2\_isr for  $\overline{\text{IRQ1}}$  and \_push\_button\_1\_isr for  $\overline{\text{IRQ0}}$ , which perform the reconfiguration of the codec.

Instead of a detailed discussion some code excerpts are listed below that illustrate the underlying principles. Nonetheless, two aspects should be emphasized. Sheet 5 of the evaluation board's schematic [6, app. B] depicts the circuit of the push buttons which reveals that a logical low is ouput in the unpressed state. Considering that the interrupt inputs are active-low, their interrupt sensitivity has to be configured for edge-sensitivity, as level-sensitivity would implicate a constant triggering of the interrupt. Further, interrupt nesting has to be disabled [7, p. 4-43 ff.], as otherwise the push button ISRs and the audio sample ISR, which implements the talkthrough by reading a sample from the ADCs and outputting them on the DACs, might interfere.

**Listing 10:** Configuration of the interrupt inputs  $\overline{IRQ0}$  and  $\overline{IRQ1}$

```

1  // Disable nested interrupts

2  bit clr mode1 NESTM;

3

4  // Enable interrupt mode for FLAGO and FLAG1

5  ustat1 = dm(SYSCTL);

6  bit set ustat1 IRQOEN | IRQ1EN;

7  dm(SYSCTL) = ustat1;

8

9  // Select edge-sensitivity for IRQO and IRQ1

10  bit set mode2 IRQOE | IRQ1E;

11

12  // Clear the interrupt latch register for IRQO and IRQ1

13  bit clr irptl IRQOI | IRQ1I;

14

15  // Unmask the interrupt IRQO and IRQ1

16  bit set imask IRQOI | IRQ1I;

17

18  // Enable interrupts (globally)

19  bit set mode1 IRPTEN;

```

In the interrupt service routines of the push buttons the volume of *all* DACs is adjusted, whereas the representative volume setting is taken from DAC1 left. The following listing depicts the ISR for the push button PB1. The ISR for push button PB2 is similar, except that the volume is decremented and the lower bound is checked.

Listing 11: Interrupt service routine for the push button PB1

```

_push_button_1_isr:

// Get current volume setting from configuration buffer

3

r14 = dm(AD1835A_REG_DACVOL1L);

r15 = AD1835A_DACVOL_MAX;

5

r14 = r14 and r15;

6

// Increase volume by 1024/10 ~= 102

r13 = 102;

9

r14 = r14 + r13;

10

11

// Check if volume is above maximum

12

r13 = r15 - r14;

13

if GE jump vol_below_max;

14

r14 = AD1835A_DACVOL_MAX;

15

vol_below_max:

```

4 APPLICATIONS Bachelor Thesis

```

17

// Set volume on all outputs

18

ad1835aSetVolume(DACVOL1L, r14);

19

ad1835aSetVolume(DACVOL1R, r14);

20

ad1835aSetVolume(DACVOL2L, r14);

21

ad1835aSetVolume(DACVOL2R, r14);

ad1835aSetVolume(DACVOL3L, r14);

23

ad1835aSetVolume(DACVOL3R, r14);

24

ad1835aSetVolume(DACVOL4L, r14);

25

ad1835aSetVolume(DACVOL4R, r14);

26

27

_push_button_1_isr.end:

28

```

# 4.2 Input Level Meter

The evaluation board provides eight general-purpose light-emitting diodes (LED) connected to the DAI, DPI and FLAG3 pin of the DSP [6, p. 1-12 f.], which allure to realize an ADC input level meter using the peak level information provided by the codec. Therefore, the LEDs are routed and a timer interrupt is set up, whereas in the timer ISR the peak level of both ADCs is read and visualized using the LEDs.

Due to the fact that the LEDs are connected to diverse interfaces of the DSP, their routing and control is not that trivial. LED8 is connected to the flag 3 pin of the DSP which is controlled through the Flag I/O register if it is configured as an output in "flag-mode" [9, p. 17-27 ff.], [7, p. B-18 ff.]. LED1 to LED5 are connected to the DPI and, therefore, may be routed to the I/O flags as well, which is visible in Figure 5. LED6 and LED7 are connected to the DAI, whereas the DAI does not offer a general-purpose register. For this reason these two LEDs are controlled by routing the desired logical level to their pin buffer input using the SRU. The code to accomplish the control of the LEDs is shown in Appendix C.

The timer of the DSP, described in [7, ch. 5], is configured by setting the timer count TCOUNT and the timer period TPERIOD. TCOUNT is decremented by one during each clock cycle. If TCOUNT reaches zero, an interrupt is generated and TCOUNT is reset to TPERIOD. For example, by utilizing Equation (3) from Section 3.3, the number of clock cycles for TPERIOD to set up a timer interrupt with an interval time of  $T_{\rm Interval} = 0.1 \, \rm s$  is determined as shown by Equation (7).

TPERIOD =

$$T_{\text{Interval}} \cdot f_{\text{CCLK}} = 0.1 \,\text{s} \cdot 331.776 \,\text{MHz} = 33177600$$

(7)

The timer generates a low priority (TMZLI) and a high priority (TMZHI) interrupt, whereas the latter is used <sup>18</sup>. A timer ISR \_timer\_isr was created and assigned to TMZHI in the interrupt vector table.

Concluding, some code excepts are depicted that illustrate the essence of the input level meter. The steps listed hereafter are performed during the startup to route and initialize the LEDs, as well as to configure and start the timer. The macros ledInitialize() and ad1835aModifySetting() are part of the software interface listed in Appendix C<sup>19</sup>.

Listing 12: Routing of the LEDs and configuration of the timer

```

// Initialize and route the general-purpose LEDs

ledInitialize();

// Enable peak level readback on AD1835A

ad1835aModifySetting(ADCPEAKRB, ON);

```

<sup>&</sup>lt;sup>18</sup>The low priority timer interrupt frequently did not get serviced, why the high priority interrupt was chosen.

<sup>&</sup>lt;sup>19</sup>Prior to these steps the PLL, serial ports, SPI port and the AD1835A codec have to be initialized.

Bachelor Thesis 5 CONCLUSION

```

// Disable nested interrupts

bit clr mode1 NESTM;

// Counter start value (start with immediate interrupt)

tcount = 0;

// Counter period in core clock cycles

tperiod = TIMER_PERIOD;

// Enable timer interrupt

bit set mode2 TIMEN;

// Clear latched high priority timer interrupt

bit clr irptl TMZHI;

// Unmask high priority timer interrupt

bit set imask TMZHI;

// Enable interrupts (globally)

bit set mode1 IRPTEN;

```

In the following the ISR for the timer interrupt is shown. The macro ad1835aUpdateLevelMeter() reads the peak level registers of the codec and sets the LEDs of the evaluation board accordingly, whereas the LED5 – LED8 is used for the left ADC and LED1 – LED4 for the right ADC. Its code is listed in Appendix  $C^{20}$ .

Listing 13: Interrupt service routine for the timer interrupt

## 5 Conclusion

In this thesis the configuration of the AD1835A audio codec chip in the context of the ADSP-21369 EZ-KIT Lite<sup>®</sup> evaluation board was discussed in-depth, whereas the involved hardware was thoroughly explored to reason and prove the correctness of every taken step. Further, two examples of use were introduced to illustrate the practical aspects of the configurable features of the codec. Moreover, these examples provided a platform for the comprehensive testing of the software interface, which exhibited a faultless operation.

This brings up the question why the code used in the DAL course mentioned in Chapter 1 occasionally exhibited erroneous behavior. That code is very rudimental and partially omits the checking of prerequisites. Considering that it is only executed once immediately after startup, this is not that dramatic. However, when its loop for sending the data frames is compared to the one presented in Section 3.6 a subtle difference can be noticed. The completion of a transfer is checked by only polling the SPIF bit which indicates if the transmit shift register is empty, whereas the TXS bit, specifying if the content of the transmit data buffer was emptied into the transmit shift register, is ignored. The exact moment when the transmit data buffer is emptied into the transmit shift register is not specified in the hardware reference, while it probably depends on the current status of the SPI clock. Anyway, it may

<sup>&</sup>lt;sup>20</sup>The thresholds for the LEDs are specified by the constant LEVEL\_THRES\_STEP defined in ad1835a.h.

BIBLIOGRAPHY Bachelor Thesis

occur that the first check of the SPIF bit is performed *before* the transmit data buffer was emptied into the transmit shift register and, consequently, the program assumes that the current transfer was finished and continues to transmit the next data frame. Therefore, the previous data frame is overwritten and lost, ending in the fact that those modifications of the configuration do not take effect.

Concluding, this thesis provided an introduction to the rather complex, yet flexible and efficient mechanism of peripheral communication using the ADSP-21369 digital signal processor. The aim of the thesis, the configuration of the AD1835A audio codec chip, yielded a convenient tool which was able to eliminate the existing problems and will hopefully find its way into practical use, being a helpful assistant in the utilization of the ADSP-21369 EZ-KIT Lite<sup>®</sup> evaluation board.

# **Bibliography**

- [1] Analog Devices Inc., Norwood. *AD1835A Data Sheet*, Revision A, Dec. 2003. http://www.analog.com/static/imported-files/data\_sheets/AD1835A.pdf.

- [2] Analog Devices Inc., Norwood. ADSP-21368 SHARC® Processor Hardware Reference, Revision 1.0, Sept. 2006.

- [3] Analog Devices Inc., Norwood. ADSP-2136x SHARC® Processor Programming Reference, Revision 1.1, Mar. 2007.

- [4] Analog Devices Inc., Norwood. *VisualDSP++ 5.0 User's Guide*, Revision 3.0, Aug. 2007. http://www.analog.com/static/imported-files/software\_manuals/719705850\_ug.pdf.

- [5] Analog Devices Inc., Norwood. ADSP-21367/ADSP-21368/ADSP-21369 Data Sheet, Revision E, Jul. 2009. http://www.analog.com/static/imported-files/data\_sheets/ ADSP-21367\_21368\_21369.pdf.

- [6] Analog Devices Inc., Norwood. ADSP-21369 EZ-KIT Lite® Evaluation System Manual, Revision 2.2, Sept. 2009. http://www.analog.com/static/imported-files/eval\_kit\_manuals/ADSP-21369%20EZ-KIT%20Lite%20Manual%20Rev%202.2.pdf.

- [7] Analog Devices Inc., Norwood. SHARC® Processor Programming Reference, Revision 2.0, Jun. 2009. http://www.analog.com/static/imported-files/processor\_manuals/ADSP\_2136x\_PGR\_rev2-0.pdf.

- [8] Analog Devices Inc., Norwood. *VisualDSP++ 5.0 Assembler and Preprocessor Manual*, Revision 3.3, Sept. 2009. http://www.analog.com/static/imported-files/software\_manuals/50\_asm\_man\_3.3.pdf.

- [9] Analog Devices Inc., Norwood. ADSP-2137x SHARC® Processor Hardware Reference, Revision 2.1, May 2010. http://www.analog.com/static/imported-files/processor\_manuals/ADSP-21367\_hwr\_rev2-1.pdf.

- [10] Freescale Semiconductor Inc. *M68HC11 Reference Manual*, Revision 6.1, 2007. http://www.freescale.com/files/microcontrollers/doc/ref\_manual/M68HC11RM.pdf.

# A Excerpts of the AD1835A Data Sheet

# A.1 Data Frames associated with the Registers

| Register Address | Register Name | Description        | Type             | Width | Reset Setting (Hex) |

|------------------|---------------|--------------------|------------------|-------|---------------------|

| 0000             | DACCTRL1      | DAC Control 1      | R/W              | 10    | 000                 |

| 0001             | DACCTRL2      | DAC Control 2      | R/W              | 10    | 000                 |

| 0010             | DACVOL1       | DAC Volume-Left 1  | R/W              | 10    | 3FF                 |

| 0011             | DACVOL2       | DAC Volume-Right 1 | R/W              | 10    | 3FF                 |

| 0100             | DACVOL3       | DAC Volume–Left 2  | R/W              | 10    | 3FF                 |

| 0101             | DACVOL4       | DAC Volume-Right 2 | R/W              | 10    | 3FF                 |

| 0110             | DACVOL5       | DAC Volume-Left 3  | R/W              | 10    | 3FF                 |

| 0111             | DACVOL6       | DAC Volume-Right 3 | R/W              | 10    | 3FF                 |

| 1000             | DACVOL7       | DAC Volume-Left 4  | R/W              | 10    | 3FF                 |

| 1001             | DACVOL8       | DAC Volume-Right 4 | R/W              | 10    | 3FF                 |

| 1010             | ADCPeak0      | ADC Left Peak      | R                | 6     | 000                 |

| 1011             | ADCPeak1      | ADC Right Peak     | R                | 6     | 000                 |

| 1100             | ADCCTRL1      | ADC Control 1      | R/W              | 10    | 000                 |

| 1101             | ADCCTRL2      | ADC Control 2      | R/W              | 10    | 000                 |

| 1110             | ADCCTRL3      | ADC Control 3      | R/W              | 10    | 000                 |

| 1111             | Reserved      | Reserved           | $R/\overline{W}$ | 10    | Reserved            |

Figure 10: Control Register Map [1, p. 19]

| Address        | R/W | RES | De-emphasis                                                  | DAC Data<br>Format | DAC Data-<br>Word Width                                       | Power-Down<br>Reset | Sample Rate                                                                       |

|----------------|-----|-----|--------------------------------------------------------------|--------------------|---------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------|

| 15, 14, 13, 12 | 11  | 10  | 9, 8                                                         | 7, 6, 5            | 4, 3                                                          | 2                   | 1, 0                                                                              |

| 0000           | 0   | 0   | 00 = None<br>01 = 44.1 kHz<br>10 = 32.0 kHz<br>11 = 48.0 kHz | 010 = DSP          | 00 = 24 Bits<br>01 = 20 Bits<br>10 = 16 Bits<br>11 = Reserved |                     | 00 = 8 × (48 kHz)<br>01 = 4 × (96 kHz)<br>10 = 2 × (192 kHz)<br>11 = 8 × (48 kHz) |

**Figure 11:** DAC Control 1 [1, p. 19]

|                   |     |     |          |                          |                    |       |                    |       |       |       |       |                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | Fu | nction |  |  |  |  |

|-------------------|-----|-----|----------|--------------------------|--------------------|-------|--------------------|-------|-------|-------|-------|--------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|--------|--|--|--|--|

|                   |     |     |          | Stereo                   | MUTE DAC           |       |                    |       |       |       |       |                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |    |        |  |  |  |  |

| Address           | R/W | RES | Reserved | Replicate                | OUTR4              | OUTL4 | OUTR3              | OUTL3 | OUTR2 | OUTL2 | OUTR1 | OUTL1              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |    |        |  |  |  |  |

| 15, 14,<br>13, 12 | 11  | 10  | 9        | 8                        | 7                  | 6     | 5                  | 4     | 3     | 2     | 1     | 0                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |    |        |  |  |  |  |

| 0001              | 0   | 0   | 0        | 0 = Off<br>1 = Replicate | 0 = On<br>1 = Mute |       | 0 = On<br>1 = Mute |       |       |       |       | 0 = On<br>1 = Mute |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |    |        |  |  |  |  |

Figure 12: DAC Control 2 [1, p. 19]

| A 11           | R/W | DEC | Function                     |

|----------------|-----|-----|------------------------------|

| Address        | K/W | RES | DAC Volume                   |

| 15, 14, 13, 12 | 11  | 10  | 9, 8, 7, 6, 5, 4, 3, 2, 1, 0 |